RESEARCH

Modulation Scheme

High speed communication Link

The ever-increasing demand for bandwidth drives the incessant development of power-efficient high-speed communication systems. The skin and dielectric losses in high-speed wireline channel require an equalizer to compensate for the intersymbol interference (ISI).

Next Generation TRX Solution

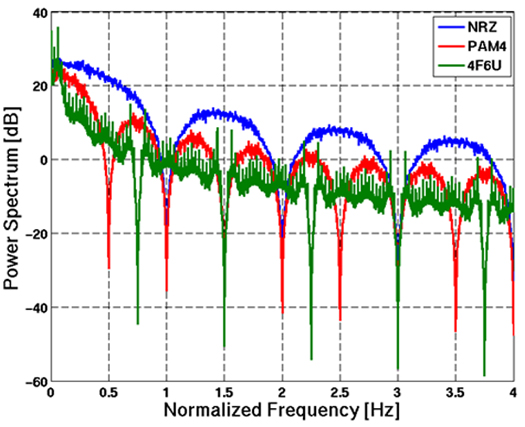

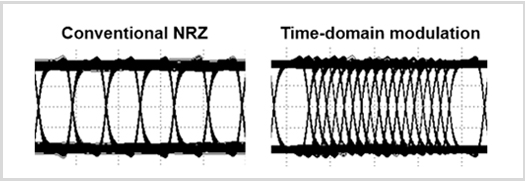

Time-domain modulation splits time for carrying more information. The divided time expands data rate compared to NRZ for equivalentoperating frequency, so it enhance spectral efficiency. This leads reduction of insertion loss on channel that lower equalization complexity can be achieved.

All-rate CDR

Emergence of new communication

standards and the backward compatibility

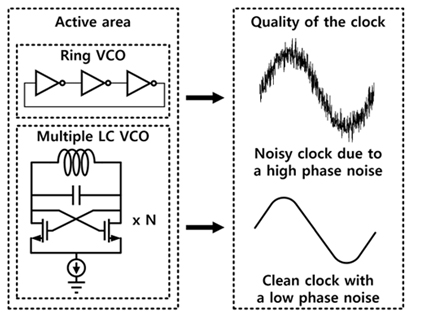

The continuous-rate CDR has been proposed to achieve the backward compatibility. Ring VCO-based CDRs are not acceptable due to the high phase noise, and multiple LC VCO-based CDRs require a large chip area.

Conventional continuous-rate CDR

The continuous-rate CDR has been proposed to achieve the backward compatibility. Ring VCO-based CDRs are not acceptable due to the high phase noise, and multiple LC VCO -based CDRs require a large chip area.

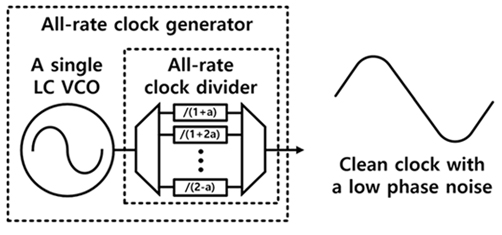

All-rate CDR with a single LC VCO

All-rate CDR with a single LC VCO supports the backward compatibility and overcomes drawbacks of the conventional continuous-rate CDR. All-rate clock ivider facilitates all-rate CDR operation with a single LC VCO. It achieves a low phase noise clock with all-rate clock frequency.

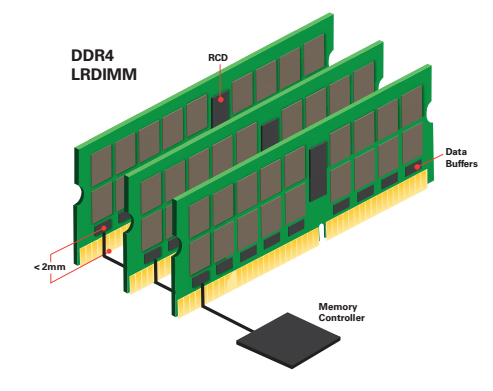

Memory Interface

Demands of Server Memory

Nowadays, as DATA for server to deal with become much larger, the server memory requires more capacities, higher speed, smaller area and lower power consumption. So far, it has been semiconductor process-downscaling that makes such specifications possible on memory. However, this approach is not suitable, lately, so that people may try another ways to satisfy more demands now and in future.

Low power High performance

Next Generation Memory Interface

Recently, there are poor signal and power integrities (SI & PI) on memory interface performance owing to the limit of trade-off: high data rate and large capacity, but small area. We are developing next generation memory interface chips which enables DIMM with more capacities, higher bandwidth due to improved SI & PI. Thus, it ill be able to be used in server computer system at the same conventional mainboard channel environment.

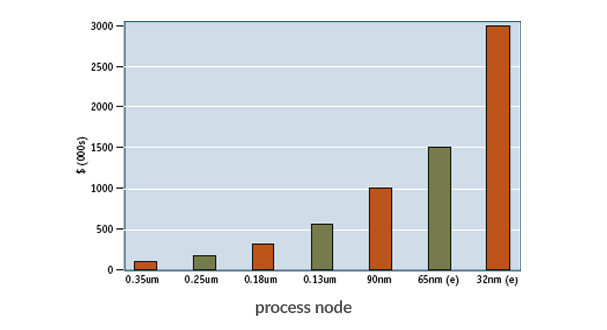

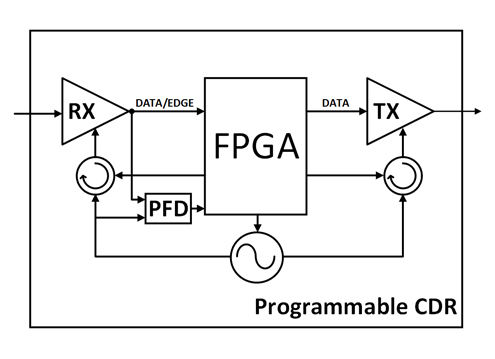

Programmable CDR

Programmable CDR

As IC fabrication minimum dimensions are getting smaller, Multi-Project Wafer (MPW) cost is significantly increased. In addition, simulation time for verifying new algorithm is big portion of total system development time. We designed programmable CDR to dramatically reduce the time and economic cost of a system development.

System Architecture

There is CDR loop including analog ASIC unit and digital FPGA unit. For using digital loop filter (DLF), the oscillator and the phase-rotators are digitally controlled. This system has many building blocks which can be turned on and off. So, we can use this system as another system¡?s building block by using appropriate combination.

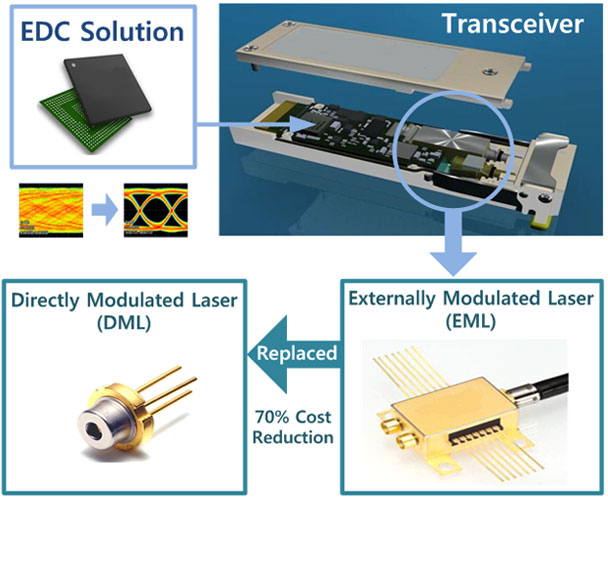

EDC

EDC (PON)

Dispersion is a problem that must be considered when transmitting signals over optical links because it introduces inter-symbol interference. By compensating for dispersion effects, our EDC extends the reach and allows low-cost DML to be used in many applications which otherwise require more expensive EML. Our technology can be combined with other circuitry in both 10- and 25-Gb/s transceiver IC designs without significant power and complexity overhead. Thus, the increased transmission distance or the significant savings in laser cost can be achieved at only modest increases in IC cost.

Silicon Photonics

Si-Photonics

Si-photonics is the silicon based optical communication solution for near future. Optical technology is very robust to electrical one in terms of loss, noise, and dispersion. However, high speed lasers are too expensive to use relatively short length comm. Modulator photonic IC which is made of silicon can replace the laser to much cheaper laser.

Next Generation TRX Solution

Si-photonics based transceiver is consist of laser, photo detector, modulator, filter, and fiber coupler. Modulators shift some phase of the light from laser. Phase-shifted light interferences with the light from other optical path on filter. This filtered light information is guided from chip to fiber. Transmitted optical signal is converted to electrical one on photo-detector.